# Twine: A Chisel Extension for Component-Level Heterogeneous Design

Shibo Chen, Yonathan Fisseha, Jean-Baptiste Jeannin, Todd Austin

University of Michigan

JTER SCIENCE & ENGINEERING

**COLLEGE OF ENGINEERING**

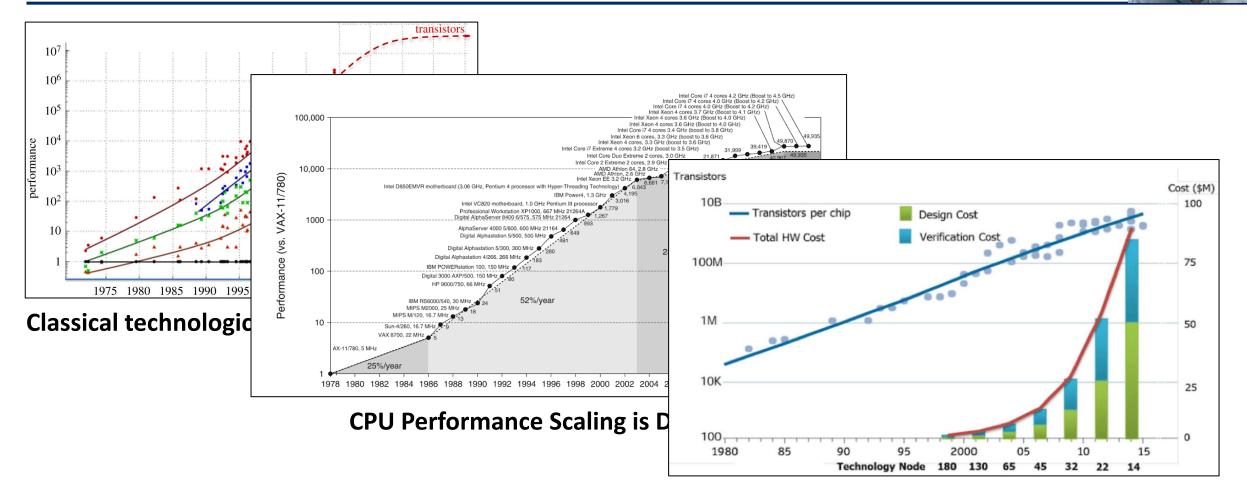

## The Death of Homogeneous Designs

#### Cost of Design is Exploding.

The future of computing beyond Moore's Law, Volume: 378, Issue: 2166, DOI: (10.1098/rsta.2019.0061)

J. Hennessy and D. Patterson, Computer Architecture: A Quantitative Approach, 6th edition, Morgan Kauffman, San Francisco, 2019.

## The Death of Homogeneous Designs

**Cost of Design is Exploding.**

The future of computing beyond Moore's Law, Volume: 378, Issue: 2166, DOI: (10.1098/rsta.2019.0061)

J. Hennessy and D. Patterson, Computer Architecture: A Quantitative Approach, 6th edition, Morgan Kauffman, San Francisco, 2019.

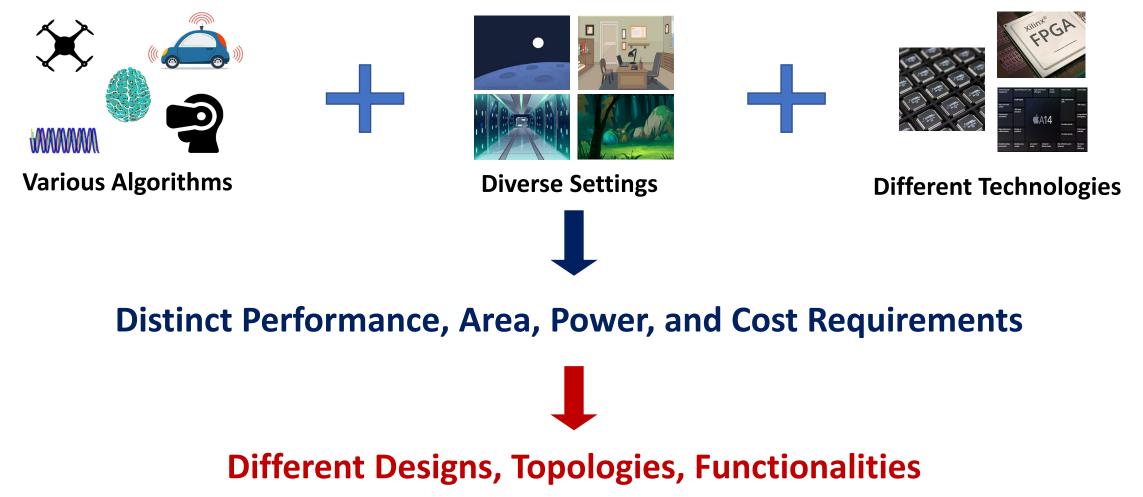

## The Era of Heterogeneous Designs

#### Increasing Amount of Hardware Designed, Customized, and Tailored for Specific Applications.

| Precision health in the palm of your hand<br>by Steve Crang, University of Michigan                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Cerebras' wafer-size chip is 10,000 times faster than a GPU<br>To foil hackers, this chip can change its code in the blink of an eye |

| Startup Rolls Out On-Device Voice<br>Command Chip That Runs on 1 mW                                                                  |

| Tesla vaunts creation of 'the best chip in the world'<br>for self-driving                                                            |

|                                                                                                                                      |

**Customized SoC**

Application-specific Hardware

## **Meeting Distinct Requirements**

## **Meeting Distinct Requirements**

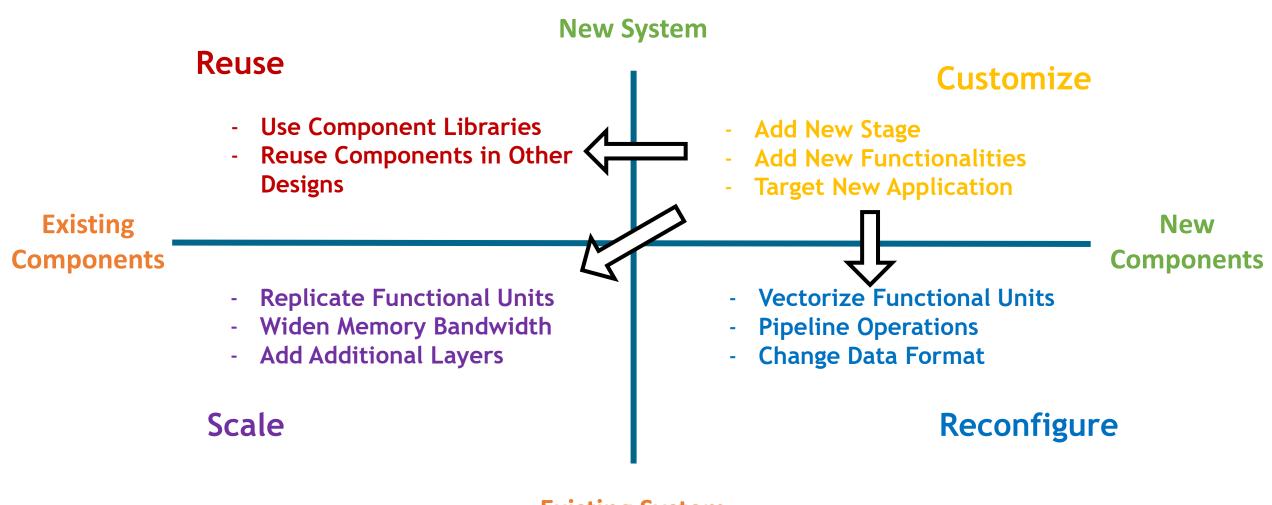

## The Zen of Heterogeneous Design

#### **Existing System**

# The Zen of Heterogeneous Design

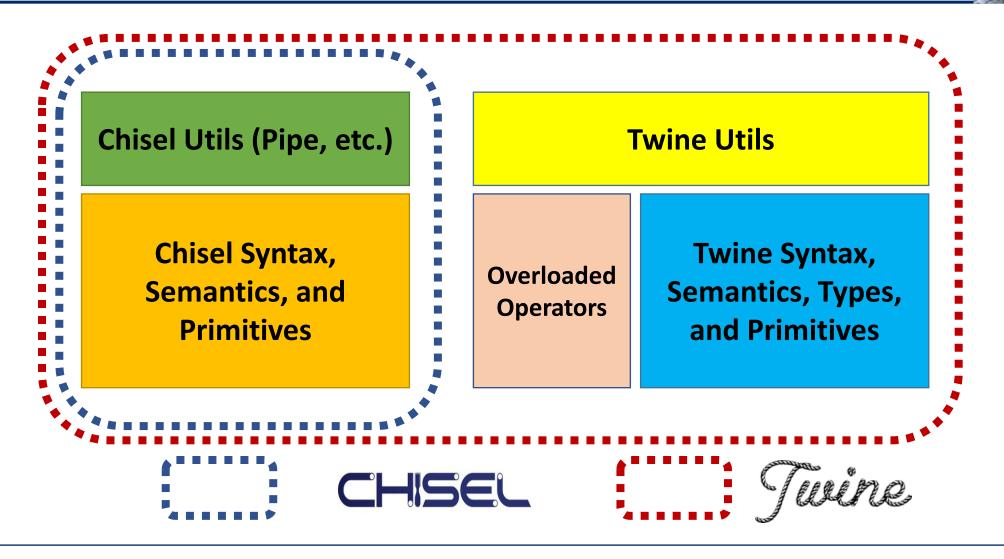

**Twine** is a Chisel extension for *component-level* heterogeneous designs.

**Twine** supports essential features for heterogeneous design:

Standardize Control Interfaces (reusability, scalability) High-level Operator for Composability (scalability, reconfigurability, customizability)

Automate Control Coordination & Data Type Conversion (scalability, reconfigurability)

Low Level Access to Chisel Primitives (reconfigurability, customizability)

#### 12

## Content

## Motivation

#### Twine Features

- Standard Control Interfaces

- High-level Operator for Composability

- Control Coordination & Type Conversion Automation

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

#### 13

## Content

### Motivation

#### Twine Features

- Standard Control Interfaces

- High-level Operator for Composability

- Control Coordination & Type Conversion Automation

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

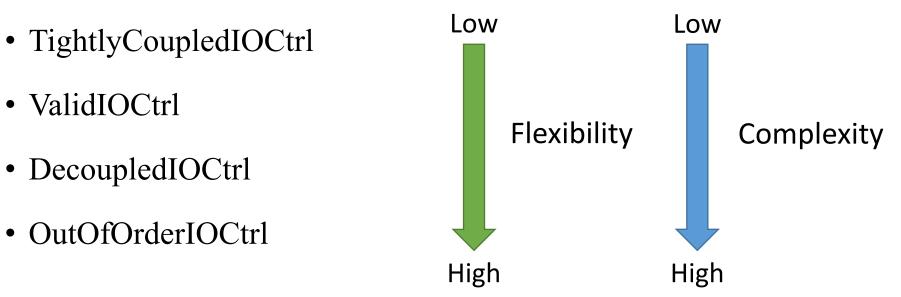

**Twine Standard Control Interfaces**

- Interfaces define how a component communicates.

- Standardizing interfaces is a common practice.

- Many standard interfaces for coarse-grained components (e.g., AXI, PCIe).

- Too heavy for intra-accelerator communication.

- Naive approach: without standard control interfaces

- Inspect, examine, and adapt component interfaces every time.

- Automation is not straightforward, requiring significant designer effort and debugging

- Better approach: standard control interfaces

- Make component behaviors more predictable.

- Enable high-level automation.

## **Twine Standard Control Interfaces**

#### Declaration of a Twine Module Interface

val in = IO(new ModuleInputType) // All data in-flow ports

val out = IO(new ModuleOutputType) // All data out-flow ports

val ctrl = IO(new ModuleCtrlType) // One of four standard control Interfaces

## • Four Standard Control Interfaces in Twine

#### 19

## Content

## Motivation

#### Twine Features

- Standard Control Interfaces

- High-level Operator for Composability

- Control Coordination & Type Conversion Automation

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

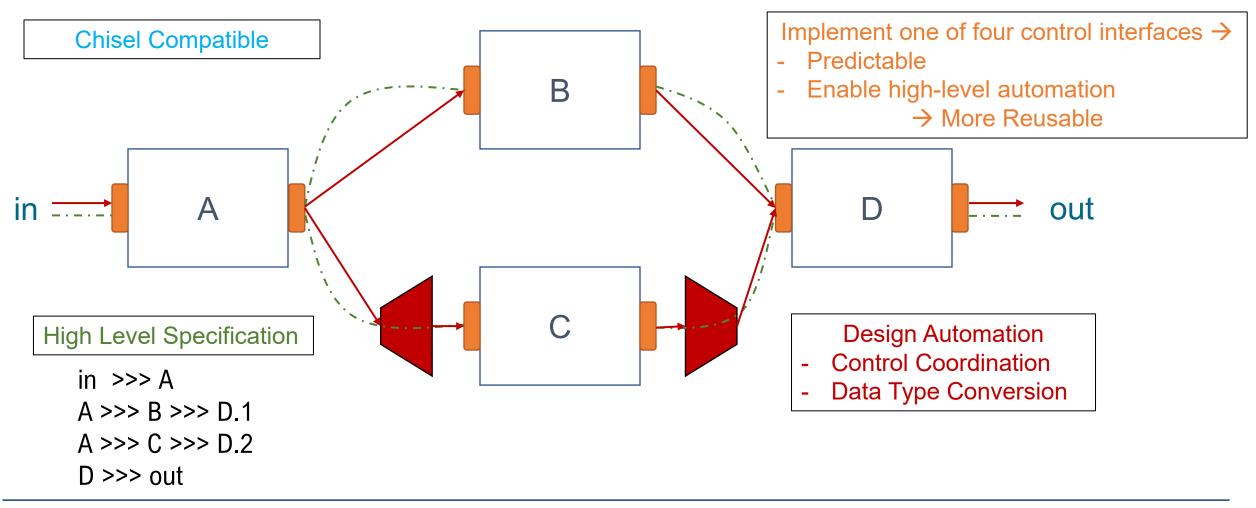

# High-level Operator for Composability

- New *flow* operator >>> to distinguish from the original Chisel wire connection

- Producer >>> Consumer

- Supports all levels of granularity

- moduleA >>> moduleB, wireA >>> wireB, Bundle(wireA, wireB) >>> moduleA

- Focus on producer/consumer relations

- *Producer:* module that outputs completed values

- Consumer: module that takes values as inputs (or needs to know when a value has been taken)

- Automatically inferred from the dataflow of the design

#### 23

## Content

## Motivation

## Twine Features

- Standard Control Interfaces

- High-level Operator for Composability

- Control Coordination & Type Conversion Automation

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

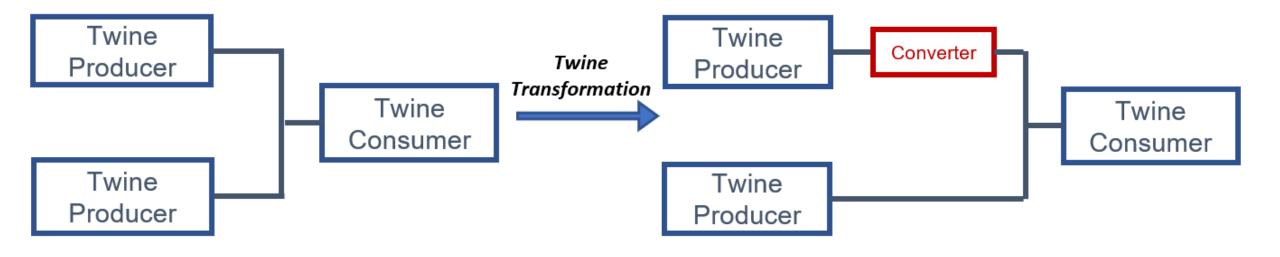

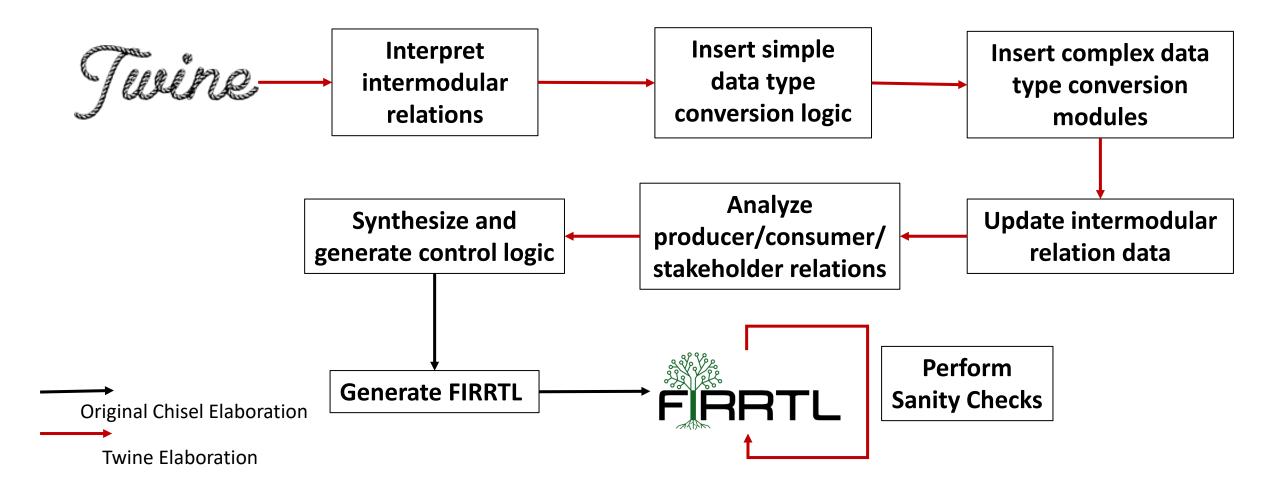

# Automate Control Coordination & Data Type Conversion

- Automatically generate system-level control logic

- Inferred based on dataflow and producer/consumer relations

- Mix-and-match across different interfaces

- Ability to manually control preserved

# Automate Control Coordination & Data Type Conversion

- Automatically generate system-level control logic

- Inferred based on dataflow and producer/consumer relations

- Mix-and-match across different interfaces

- Ability to manually control preserved

- Data Type Conversion

- Auto conversion between different data types (*e.g.,* floating points <-> integers)

- Auto conversion between different port width (useful for vectorized components)

## Automate Data Type Conversion

- Simple conversion logic is combinational and transparent

- e.g., Unsigned Integers <-> Signed Integers, Bitwidth expansion

- Complex conversion logic serves as a full converter module

- Floating point to integer conversion

- Serializer and de-serializer for vectorized components

## Put Them Together

Assume there are modules A, B, C, and D. Module C is a vector module.

- Motivation

- Twine Features

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

Build Upon Existing Infrastructure & Preserve All Features

## **Twine Elaboration Pipeline**

## Content

- Motivation

- Twine Features

- Implementation & Circuit Generation

## • Experiments & Results

- Productivity Improvement Experiment

- Design Quality Experiment

- Limitations & Future work

- Conclusion

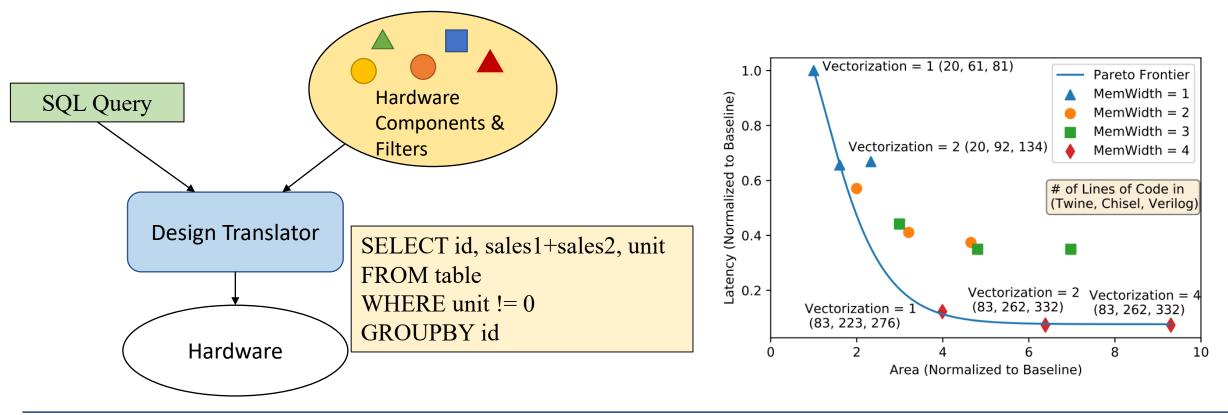

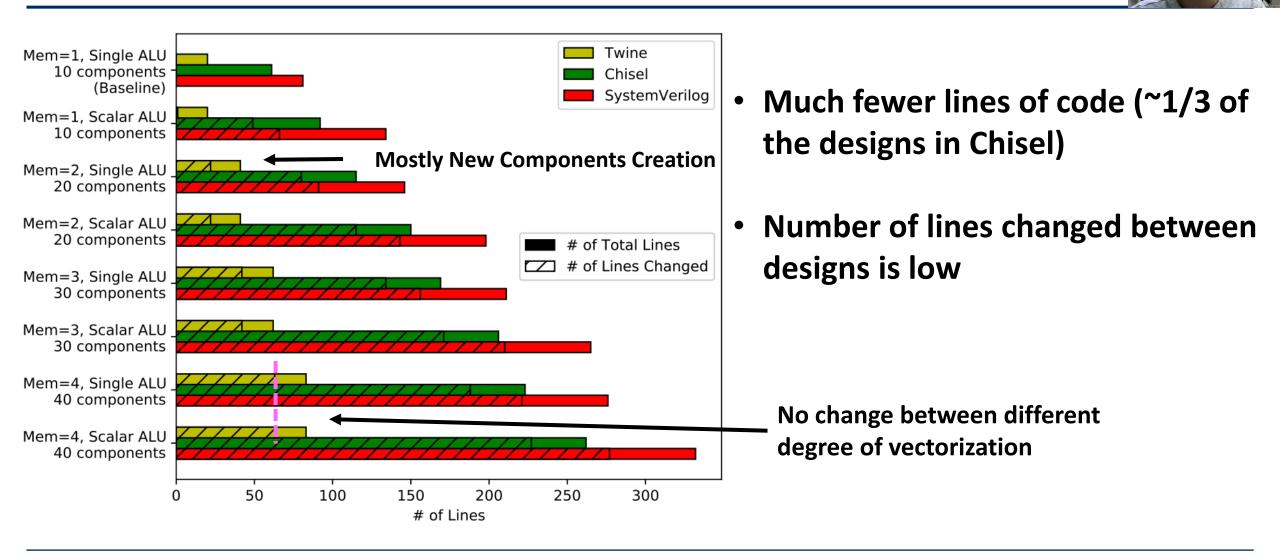

# **Experiment: Productivity Improvement**

- Prototyped a database query accelerator similar to Q100 (ASPLOS '14)

- Conducted design space exploration in Verilog, Chisel, and Twine

## **Experiment: Productivity Improvement**

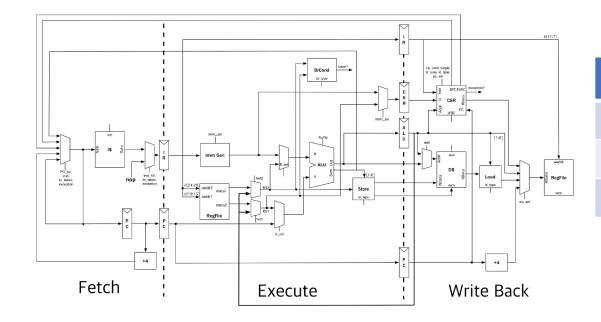

# **Experiment: Design Quality**

- Reproduced RISCV-MINI, a three-stage RISCV core in Twine

- Components interfaced with DecoupledIOCtrl

|        | Area*     | Clock Period* |

|--------|-----------|---------------|

| Chisel | 727004.94 | 0.85 ns       |

| Twine  | 725937.90 | 0.82 ns       |

| Change | -0.14%    | -3.5%         |

RISCV-MINI: https://github.com/ucb-bar/riscv-mini

\*Based on IBM 45nm CMOS Process

- Motivation

- Twine Features

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

Inflexible processing granularity for vectorized modules

- Missed opportunities in inter-module optimizations

- Possible out-of-order execution or forwarding across the module boundary

## Better verification and debugging capabilities for Twine

• Utilize the producer/consumer relations to speed up verification process

## • Flexible & customizable interface protocol framework

• User-defined interfaces and elaboration process

- Motivation

- Twine Features

- Implementation & Circuit Generation

- Experiments & Results

- Limitations & Future work

- Conclusion

## Conclusion

wine,

#### • Twine is a Chisel extension that supports

- reusable standard component control interfaces

- high-level operator for composability

- control coordination & data type conversion automation

- Twine boosts developer productivity for heterogeneous designs.

- 1/3 of lines of codes compared to Chisel

- Twine provides similar design quality comparing to Chisel.

- Visit <u>https://github.com/Twine-Umich/Twine</u> to download Twine.

Twine is an open-source project.

To download Twine, please visit <a href="https://github.com/Twine-Umich/Twine">https://github.com/Twine-Umich/Twine</a>

All feedbacks are welcomed!